# Relazione DAC, Sample&Hold, ADC

<u>Obiettivo</u>: studiare e simulare le principali configurazioni di convertitori (analogici a digitali e viceversa), di dispositivi campionatori e di registri a successive approssimazioni.

### DAC – Digital to Analog Converter

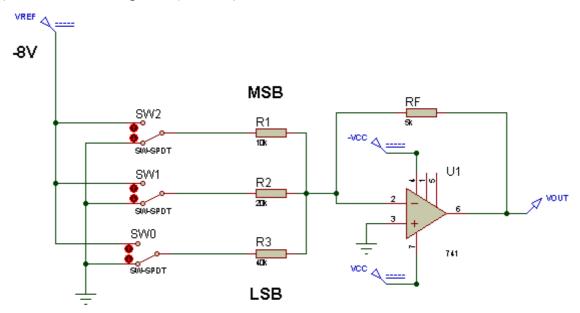

### 1) DAC a resistori pesati (a tre bit)

Tale convertitore è un semplice sommatore invertente che somma le varie correnti in ingresso; ogni ramo ha una resistenza il doppio della precedente, facendo in modo che le correnti vadano via via a dimezzarsi. In questo modo ogni corrente rappresenta il contibuto del bit (più o meno significativo). La resistenza di retroazione è la metà rispetto a quella del ramo del MSB, in modo che quest'ultimo "pesi" la metà rispetto alla tensione di riferimento. Così facendo la tensione massima di uscita è data da

$$Imax = -\left(\frac{Vref}{R} + \frac{Vref}{2R} + \frac{Vref}{4R}\right) =$$

$$= \frac{-Vref}{R} \cdot \frac{4 + 2 + 1}{4} = -\frac{7}{4} \cdot \frac{Vref}{R}$$

$$Vout \, max = -Imax \cdot \frac{R}{2} = \frac{7}{8} \, Vref$$

ovvero la tensione di riferimento meno un quanto.

Questo convertitore è molto limitato perchè se la resistenza di feedback (la più piccola) vale  $1[k\Omega]$ , il numero massimo di altri rami è nove perchè la resistenza maggiore varrà  $512[k\Omega]$ , ed un decimo ramo richiederebbe una resistenza di  $1024[k\Omega]$  che supera il limite massimo che garantisce la linearità di guadagno.

Il quanto vale 1 [V].

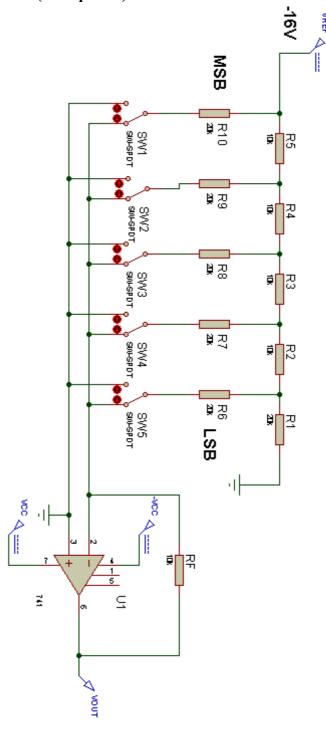

## 2) DAC con rete a scala (a cinque bit)

Con questa configurazione in ogni ramo scorre sempre la stessa corrente (che va a dimezzarsi più ci si avvicina a destra) che viene poi "indirizzata nel ramo di feedback e sommata alle altre o verso massa. Il generatore di tensione di riferimento "vede" due rami dalla resistenza ognuno di  $20[k\Omega]$  (in questo schema) e la corrente si dimezza ad ogni nodo. Potenzialmente, questo schema permette di avere infiniti bit in ingresso perchè la resistenza totale dal punto di vista del generatore è sempre la stessa.

Il quanto in questo caso vale 0.5[V]

Un circuito S/H solitamente è fondamentale per eseguire una corretta conversione analogico/digitale perché, per permettere al convertitore AD di eseguire una corretta conversione, il segnale in ingresso all' ADC deve rimanere costante per tutta la durata del tempo di conversione dell' ADC. Ragionando possiamo intuire che, se il segnale d'ingresso ha una frequenza massima di variazione molto più piccola dell' inverso del periodo di conversione dell' ADC, non è necessiario l'impiego di un sample and hold nella conversione AD. Un esempio di segnale molto lento nella sua variazione potrebbe essere un segnale ricevuto da un sensore per la misurazione di una temperatura ambientale.

Un circuito di Sample & Hold ideale è composto da due blocchi principali, il primo è la parte di comando composta da un circuito che abilita il passaggio del segnale d'ingresso al S/H, e il secondo blocco è un condensatore il quale memorizzsa il valore di tensione ricevuto in ingresso una volta abilitato il circuito di comando. Esistono anche dei circuiti particolari denominati track and hold che hanno la caretteristica di avere il comando di abilitazione del sample and hold attivo solamente per il periodo necessario per l'acquisizione del segnale dell' ADC.

I sample and hold reali sono composti da 4 principali componenti:

- L'amplificatore / buffer d'ingresso.

- Il dispositivo che si occupa dell' immagazzinamento dell'energia nella fase di hold, un condensatore.

- Il buffer in uscita dal sample and hold. (Si utilizza un buffer in uscita dal sample and hold in modo da poterlo adattare ad un altro circuito perché l'impedenza vista dall'uscita di un buffer è molto bassa e per permettere al condensatore, utilizzato per la fase di hold, di mantenere l'energia dato che l'impedenza vista sull'ingresso di un buffer è molto alta)

- Il circuito di switching, utilizzato per l'abilitazione della fase di hold.

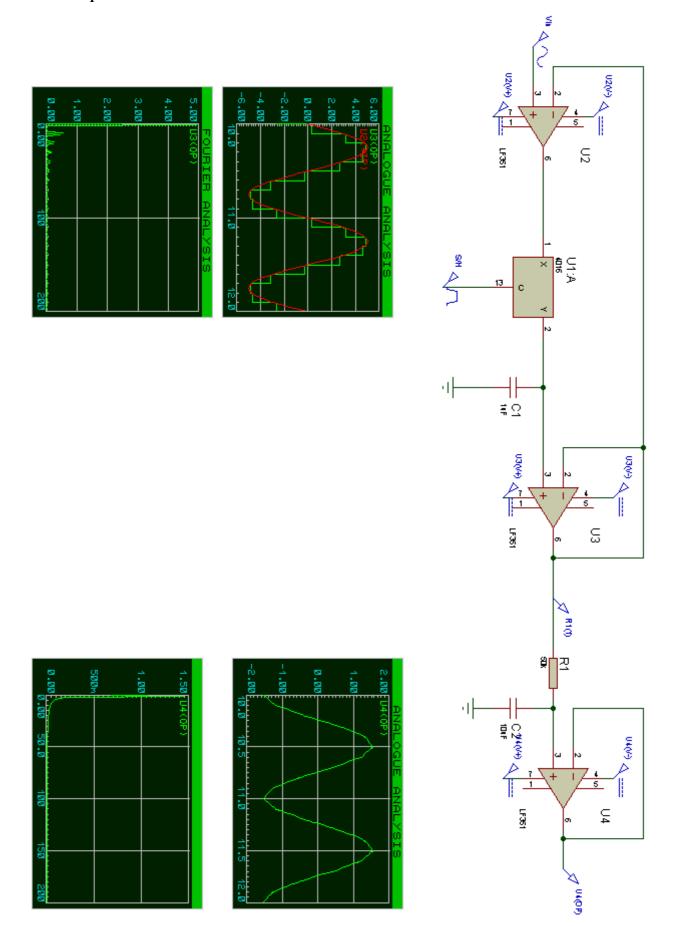

E' raffigurato nello schema un dispositivo campionatore di segnale seguito da un filtro attivo (con guadagno statico circa uguale a 1 essendo un buffer) passa-basso che mostra l'eliminazione delle armoniche a frequenza maggiore createsi nello spettro del segnale per via della modulazione PAM (campionamento).

L'uscita del filtro è sfasata di 90° rispetto all'ingresso per via della componente capacitiva del filtro.

La configurazione di tale circuito di Sample & Hold ha i vantaggi e gli inconvenienti degli amplificatori controreazionati.

Tra i vantaggi vi è la diminuzione degli errori e dell'influenza dei disturbi, garantendo una precisione più elevata. L'inconveniente di questo circuito è il maggiore tempo di acquisizione e di assestamento richiesto dovuto alla struttura ad anello chiuso.

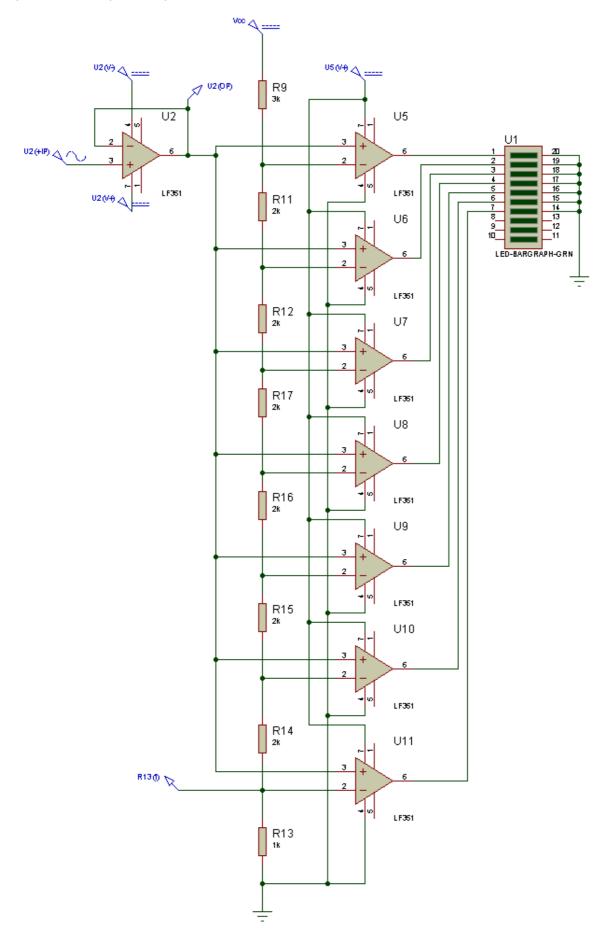

L'A/D flash permette una conversione immediata del dato analogico in ingresso poiché la tensione viene confrontata con varie soglie prelevate da un partitore di tensione.

Bastano sette soglie perchè lo stato in cui tutti i comparatori danno in uscita uno stato basso vale come combinazione minima (000). Con un decoder apposito possiamo facilmente avere in uscita il codice binario desiderato.

La resistenza della soglia minore è dimezzata rispetto alle altre in modo che l'errore sia il minimo (q/2). La resistenza che collega la soglia maggiore con la tensione di riferimento è 3/2 rispetto alle altre in modo che la soglia massima corrisponda a Vref-q.

Abbiamo utilizzato un buffer tra il generatore e l'A/D vero e proprio in modo da avere una resistenza d'uscita molto bassa. In realtà, il quanto non è sempre costante e varia leggermente in funzione della tensione d'ingresso.

Con un ingresso sinusoidale unipolare è possibile notare l'accendersi e lo spegnersi dei vari led che indicano le rispettive soglie.

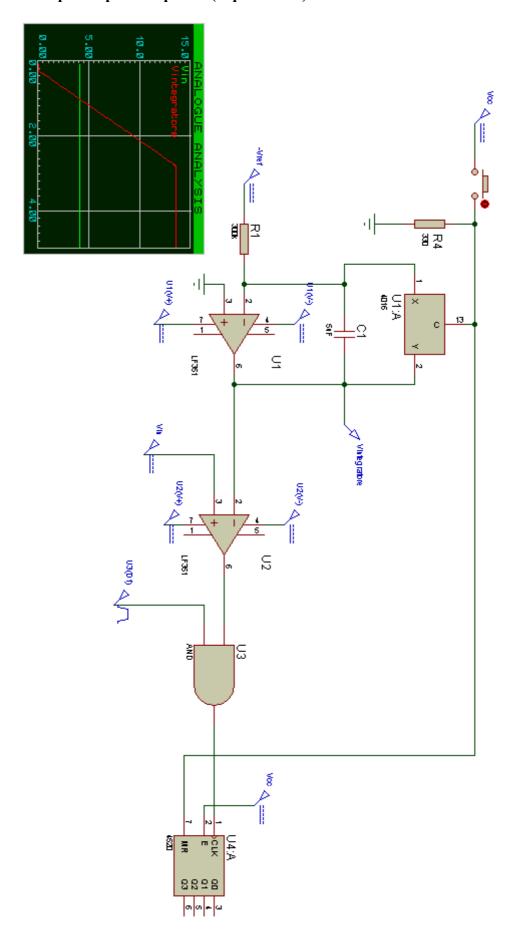

## 2) A/D a rampa semplice unipolare (a quattro bit)

Tale convertitore analogico/digitale si basa sul confronto della tensione in ingresso con una rampa di tensione crescente generata da un integratore.

Presentando il circuito una parte costituita da un integratore invertente, mettendo in ingresso una tensione di riferimento negativa la rampa sarà, appunto, positiva.

L'uscita dell'integratore è quindi

$$Vu = \frac{Vref}{RC} \cdot t$$

con pendeza uguale al coefficiente costante del tempo (nella formula).

Finchè l'uscita dell'integratore è minore della tensione da convertire, il comparatore dà in uscita uno stato alto che funge quindi da gate per il segnale di clock che viene inviato direttamente al contatore. La pendenza della rampa e la frequenza del clock devono essere in stretta relazione per dare il funzionamento desiderato in uscita.

Un contatore binario crescente conteggia gli impulsi finchè la rampa non ha raggiunto il valore da convertire, dopo il quale blocca l'invio del clock al contatore.

Con il comando di SOC viene scaricato istantaneamente il condensatore dell'integratore e resettato a zero il contatore.

Il numero di conteggi per arrivare ad una certa tensione in ingresso Vi è dato da

$$N = \frac{Vi \cdot RC \cdot fck}{Vref}$$

dove RC è la costante di tempo dell'integratore e fck è la frequenza di clock in ingresso.

I vantaggi sono il costo basso, la semplicità strutturale e l'elevata risoluzione.

Gli inconvenienti di questo dispositivo sono la scarsa precisione e stabilità, direttamente dipendenti dalla costante di tempo dell'integratore e dalla frequenza del clock (che potrebbero variare leggermente nel tempo). Il tempo di conversione è elevato e dipende dal valore di tensione analogica in ingresso.

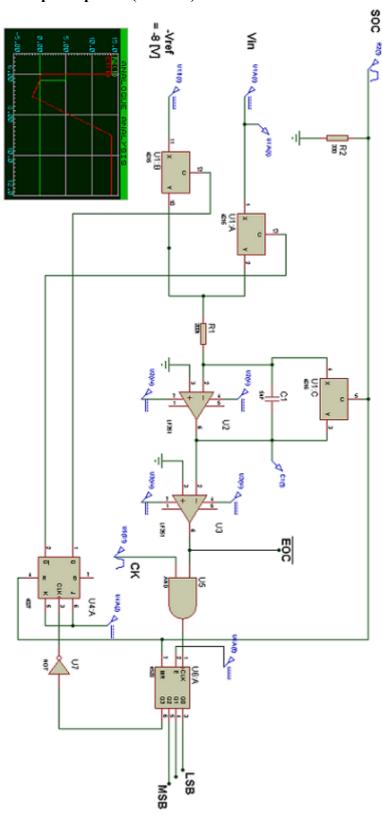

## 3) A/D a doppia rampa unipolare (a tre bit)

Se attivato il segnale di SOC viene resettato il contatore binario, scaricato il condensatore e resettato il flip flop JK. Sul fronte di discesa viene collegata la tensione da convertire, che genera quindi una rampa negativa decrescente con pendenza  $\frac{Vi}{RC}$ .

L'uscita del comparatore è alta per tutto questo tempo poiché la massa è a potenziale maggiore: il contatore inizia a contare fino all'impulso 2^n dove n è la risoluzione del convertitore uguale al numero di stadi del convertitore. Il passaggio allo stato alto del MSB causa la commutazione

(toggle) del flip flop che in uscita abiliterà la tensione di riferimento negativa (inviata come ingresso all'integratore). Tale tensione genera una rampa crescente durante la quale il conteggio parte da 0 (il MSB del contatore non è considerato come uscita del convertitore) che si blocca solo quando la tensione dell'integratore raggiunge il valore dell'ingresso non invertente (0 [V]). Il terminale attivo basso EOC segnala così la fine della conversione.

Nella prima fase, l'uscita dell'integratore è data da

$$Vu = -\frac{Vi}{RC} \cdot t$$

la quale raggiunge un valore minimo -Vm quando il tempo è uguale a 2<sup>n</sup>\*Tclock

$$-Vm = -\frac{Vi}{RC} \cdot 2^n \cdot Tclock$$

La parte di rampa crescente ha invece equazione

$$Vu = -Vm + \frac{Vref}{RC} \cdot t$$

Questa raggiunge il valore 0 all'istante N\*Tclock

$$0 = -Vm + \frac{Vref}{RC} \cdot N \cdot Tclock$$

Mettendo assieme le due equazioni principali

$$0 = -\frac{Vi}{RC} \cdot 2^{n} \cdot Tclock + \frac{Vref}{RC} \cdot N \cdot Tclock$$

$$0 = \frac{Tclock}{RC} \left( -Vi \cdot 2^{n} + Vref \cdot N \right)$$

Per cui

$$-Vi \cdot 2^n + Vref \cdot N = 0$$

$$Vref \cdot N = Vi \cdot 2^n$$

Da cui ricaviamo l'equazione principale del convertitore (il numero di conteggi che deve essere fatto per convertire il dato):

$$N = \frac{Vi \cdot 2^n}{Vref}$$

Capiamo immediatamente come la precisione non dipenda dai potenziali fattori instabili del convertitore quali Tclock e costante di tempo dell'integratore (N non dipende infatti da queste).

Di contro, il tempo di conversione è molto elevato e dipendente dalla tensione da convertire ed esistono alcuni errori legati alla tensione di offset degli operazionali (recuperabile con un trimmer collegato agli appositi pin).

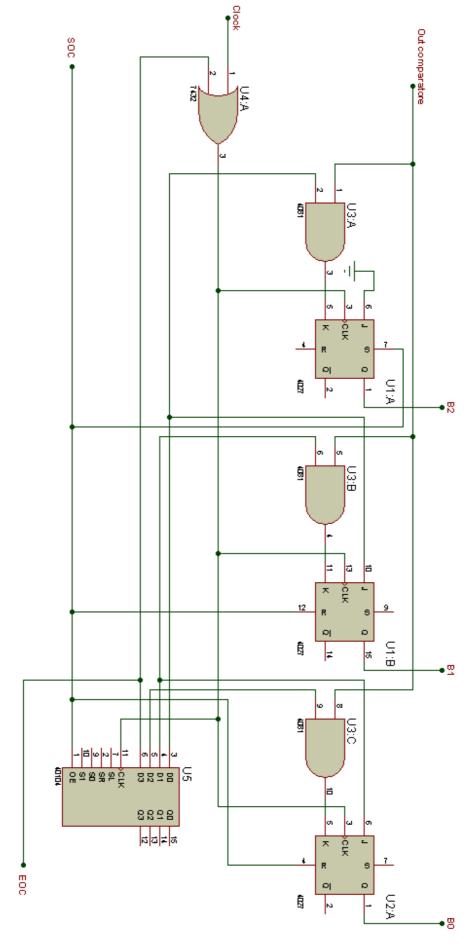

## 4) SAR – Registro a successive approssimazioni (a quattro bit)

Abbiamo analizzato solamente il funzionamento interno di un registro a successive approssimazioni per quanto riguarda i convertitori a retroazione, poiché facilmente schematizzabile. Le configurazioni a gradinata e a successive approssimazioni sono facili da schematizzare ma più complesse da simulare tramite Proteus.

Lo shift register PIPO (parallel input parallel output) programmabile tiene in memoria un certo "pattern" o combinazione. Con il comando di start il patter viene trasferito sui piedini D0-3 che ad ogni colpo di clock viene shiftato di un bit.

Se l'uscita del comparatore è alta (l'uscita del DAC supera la tensione d'ingresso) e il bit precedente shiftato era allo stato alto viene attivato il comando K (equivalente al reset dell'uscita del flip-flop).

In questo modo viene effettuata una ricerca dicotomica che minimizza le operazioni di conversione alla quantità di bit del dispositivo stesso. Quando il bit shiftato raggiunge l'ultimo pin (D3) la conversione viene bloccata bloccando il clock; il pin D3 funge anche da EOC.

Note e conclusioni: Grazie alle simulazioni siamo riusciti a "toccare con mano" le caratteristiche e le limitazioni reali dei convertitori analogici/digitali e viceversa, studiando anche alcuni dispositivi come il S/H e il SAR. Abbiamo deciso di non sviluppare anche gli schemi del convertitore a gradinata e a successive approssimazioni per la difficoltà di simulazione ed il grande tempo da dedicare a queste esperienze.

Confrontando tra loro i vari convertitori è più facile capire quando conviene utilizzarne uno rispetto ad un altro, quali per il costo, quali per la velocità di conversione e quali per l'elevata precisione. In generale, abbiamo capito che il convertitore a successive approssimazioni è spesso il più efficiente, trovabile facilmente in circuiti integrati appositi.